|

3485| 4

|

PCB防静电设计的必要性 |

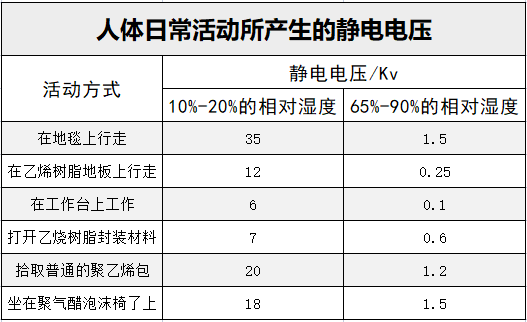

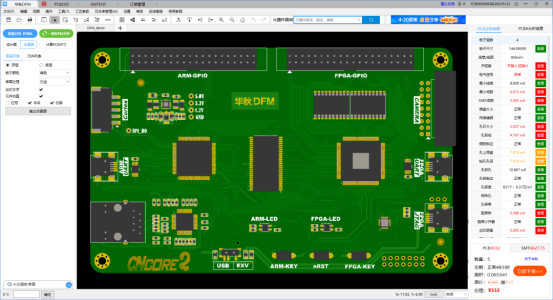

下图大致列举了一下不同行为产生的静电电压大小:  一、静电是如何产生的 静电是一种电能,它存在于物体表面,是正负电荷在局部失衡时,产生的一种现象,如摩擦起电就是一种静电放电现象。 静电的问题一直困扰着许多电子产品,其放电电流产生的电磁场,通过电容耦合、电感耦合或空间辐射耦合等途径,对电路造成了严重干扰,所以我们在PCB设计初期,就必须考虑到静电的防护问题。 下图是关于静电产生的示意图:  二、PCB如何设计防静电 PCB布局的原则,一般尽可能将静电保护器件靠近输入端或者连接器,静电保护器件与被保护线之间的线路距离,应该设计得尽量短一些。对于PCB设计来说,在容易发生静电放电的边缘,设置一定的隔离距离非常重要,对于机架类产品,每千伏的静电电压的击穿距离在1mm左右,如果在容易放电的边缘设置一个3-5mm隔离区,就可以抵抗3-5Kv的静电电压。 1、低速板静电防护设计 1) 走线需横平竖直,尽量减少信号线路并排走线; 2) 如果空间允许的话,走线越粗越好; 3) 按照高速电路设计理念来进行布线; 4) 避免在PCB边缘处理重要的信号线,如时钟、复位信号等; 5) 所有PCB板的传导环路,包括电源和地线环路,应该尽量小; 6) 单面或双面板,在没有电源平面的情况下,电源走线旁边必须要跟随一根地线; 7) 尽量使用多层板布线。 2、高速板静电防护设计 1) 走线需要有良好的地平面; 2) 保持足够的间距,如滤波器、光耦、交流电源线与弱信号线; 3) 长距离走线加低通滤波器(C、静电器件、RC、LC); 4) 隔离(增加屏蔽罩),避免被保护的导线与未被保护的导线并排走线; 5) 避免与其他器件使用同一条回路来连接公共接地点。 3、防止出现静电的通用办法 1) 保持地的完整,加大地的泄放面积,平整地铺铜均匀,保持地的电阻值不变,互相之间水平状态地平面平稳; 2) 板外围进行环绕地设计,数据线用地包围; 3) 地孔越多越好,并使每层地紧密连合在一起; 4) 在PCB上安装光耦合器或者变压器,以及结合介质隔离和屏蔽,都可以很好的抑制静电放电冲击; 5) 可将PCB的GND与外壳地进行单点接地,防止静电放电电流在机箱上产生的电压耦合进电路,但需注意接地点的选择,选择在电缆入口处接地; 6) 如果PCB面积允许,并且整机系统的搭接、静电泄放通道都很好,可以在PCB周围设置接地防护环,可裸铜处理,并采用很多过孔连接。 三、防静电设计的可制造性检查 这里推荐一款国产免费的PCB和PCBA检测软件:华秋DFM,它对于可制造性检查领域来说非常专业,其检测参数也是可以随着设计者的实际需求进行调整的,根据不同板厂的工艺标准进行生产前的隐患提示并给出最优的修改建议,虽然对上文所讲的PCB防静电设计性能没有做对应的检查项,但是可以检查PCB设计图中防静电设计的位置是否存在可制造性风险等。  术业有专攻,防静电处理的问题,工程师们在PCB走线布局和结构接口方面做好防护措施即可,对于可制造性与可组装性的问题,可以交给专业的华秋DFM软件解决!有需要可以访问官网下载体验。 |

沪公网安备31011502402448

沪公网安备31011502402448© 2013-2026 Comsenz Inc. Powered by Discuz! X3.4 Licensed