|

1230| 0

|

LattePanda MU载板设计指南 |

|

LattePanda MU载板设计指南 LattePanda Mu 载板设计指南系列|前言 我们刚刚发布了 第一节:前言与基础指南,帮你快速了解 Mu 计算模块、引脚布局、HSIO 多路复用以及高速 PCB 设计要点。 前言 本指南旨在为硬件工程师提供关键的设计规则和建议,帮助你更高效地动手设计。 注意:只适用于搭载 Intel N100 或 N305 处理器 的 LattePanda Mu 计算模块。 引脚说明 LattePanda Mu 的边缘连接器密度高、功能多,我们把详细引脚介绍放在了单独文档里。 HSIO 多路复用 Mu 的高速 I/O 通道很灵活,但配置要注意:

PCB 设计要点

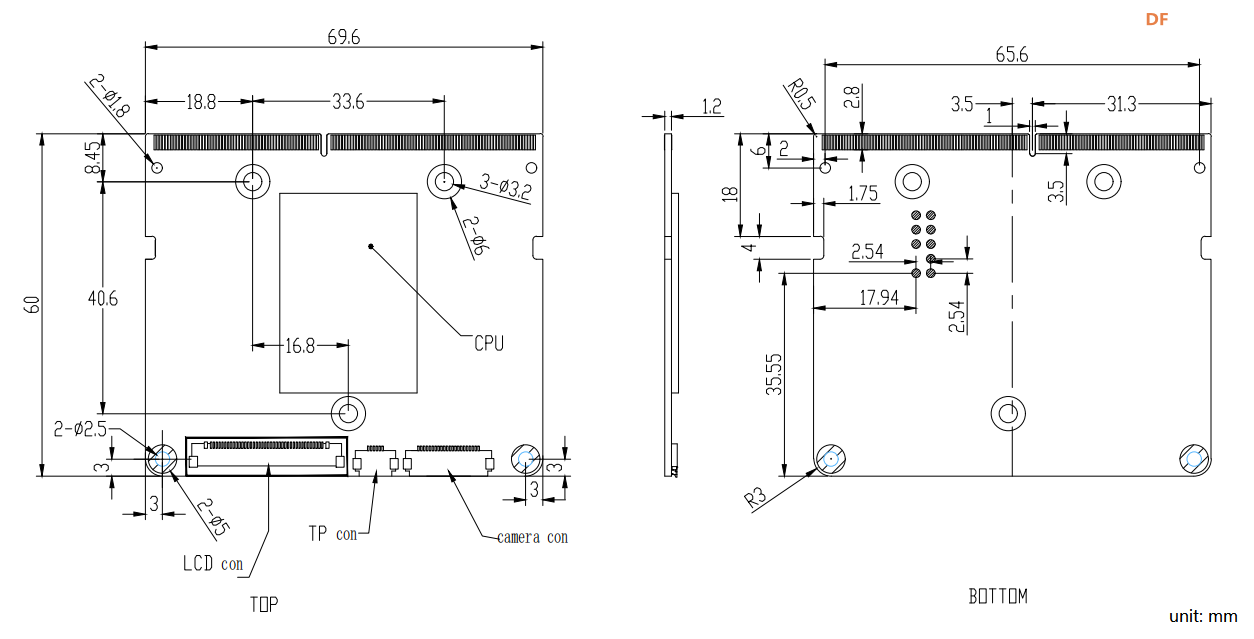

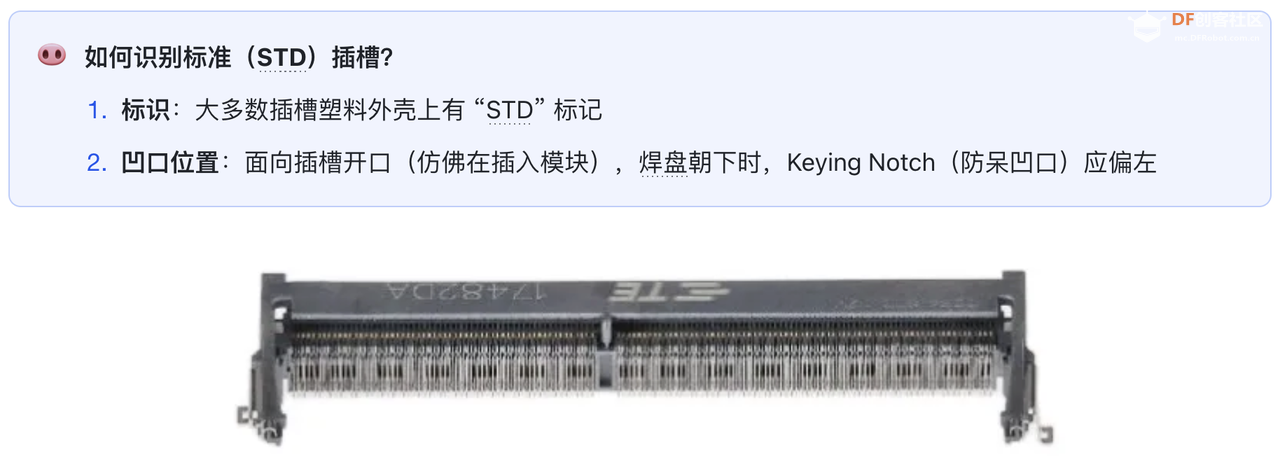

点此查看 LattePanda Mu 载板设计指南系列|边缘连接器 这一节我们聚焦 边缘连接器,教你如何正确选择和安装 DDR4 SODIMM 插槽,让 Mu 模块与载板完美契合。 LattePanda Mu x86 计算模块采用 260 针边缘连接器,在物理上兼容标准笔记本 DDR4 SODIMM 内存插槽。 引脚说明 由于 LattePanda Mu 计算模块具有高密度边缘连接器和多功能引脚定义,我们将详细引脚说明整理到 LattePanda Mu 引脚文档 中。 机械规格

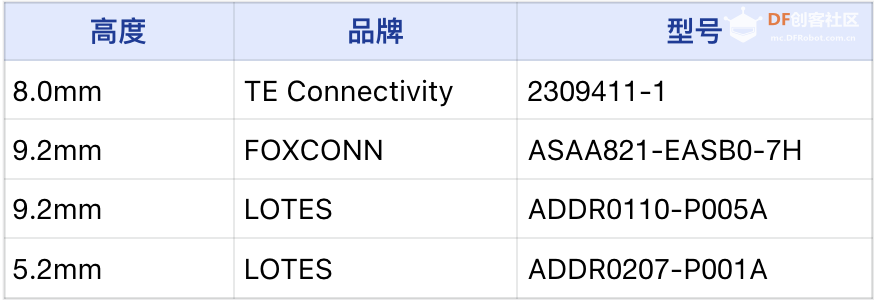

插槽选择指南 虽然 Mu 模块兼容标准 DDR4 插槽,但为了确保机械和电气匹配,需要严格遵守以下规则: 关键规则

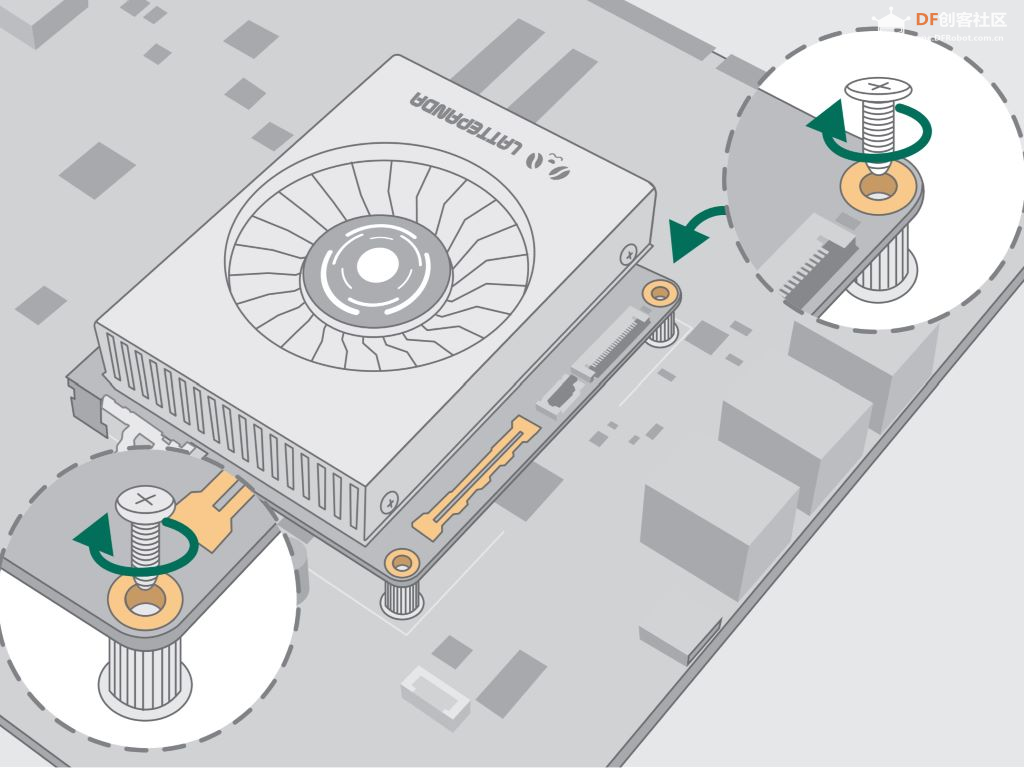

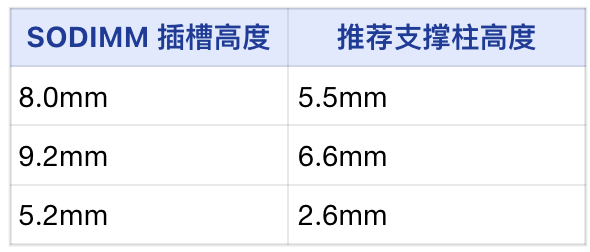

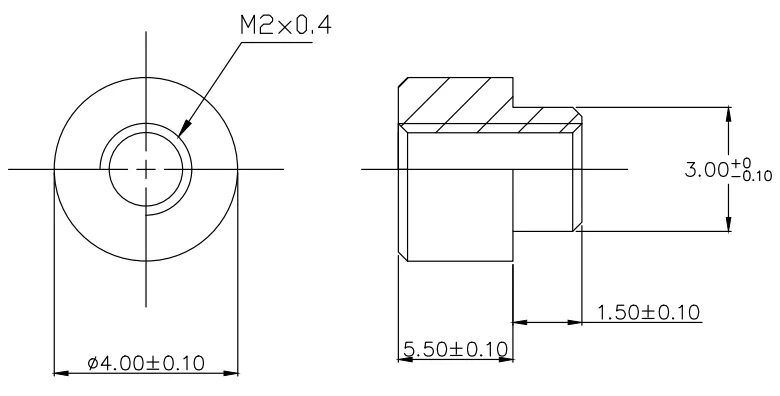

可焊支撑柱选择  将 LattePanda Mu 插入 SODIMM 插槽后,必须使用螺丝和垫片将其固定到载板上。载板上的垫片高度必须与 SODIMM 插槽高度相匹配,以确保计算模块平整安装

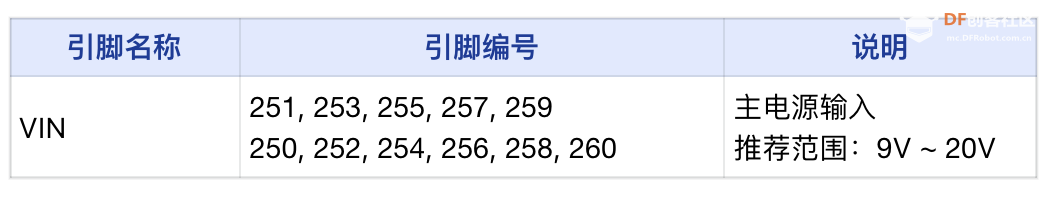

在 DFR1142 Lite 载板 上,DDR4 插槽高度为 8.0mm,因此支撑柱高度为 5.5mm,固定螺丝直径为 2mm。  LattePanda Mu 载板设计指南系列|电源 本节聚焦电源,包括电压范围、引脚连接以及功率余量规划,确保你的载板在各种应用场景下都能稳定运行。 LattePanda Mu x86 计算模块采用宽电压输入设计。为确保系统稳定运行,请严格遵循以下电源设计规范。 电压要求  在不使用 eDP 显示屏的情况下,为获得最佳兼容性和安全性,强烈建议将输入电压保持在 9V–20V 之间。 使用 eDP 显示屏时,最大供电电压将受 eDP 屏本身限制。 在 LattePanda Mu 计算模块的硬件设计中,eDP 显示屏转换器的电源直接连接到系统主电源轨,中间没有任何降压电路。 因此,如果你的设计中包含连接到 LattePanda Mu 的 eDP 显示屏,整个系统允许的最大输入电压将由 eDP 显示屏转换器的最大输入电压决定。 连接指南 引脚定义  由于 GND 引脚数量较多,此处不逐一列出,请参考 LattePanda Mu 引脚文档。 引脚连接方式 为降低阻抗并支持大电流:

功率预算 电源设计必须预留足够的功率余量。在不包含载板外设功耗(如高功率 USB 设备、PCIe 扩展卡等)的情况下,使用默认 BIOS 固件时,计算模块本身的最低功耗需求为:

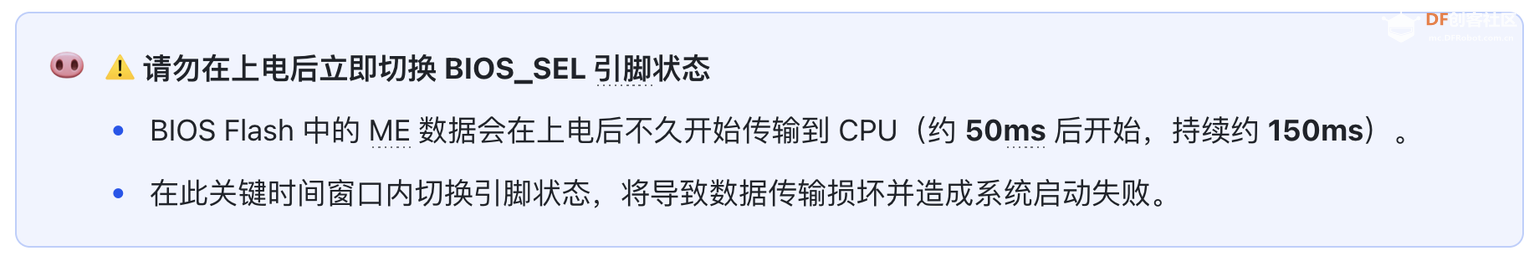

以上数值为最低要求,可能会对性能产生影响。 LattePanda Mu 载板设计指南系列|Dual BIOS 本节聚焦 Dual BIOS 机制,介绍如何通过 BIOS_SEL 引脚在模块内置 Flash 与载板外部 Flash 之间切换启动源,从而实现更灵活的 BIOS 定制与调试。 LattePanda Mu 支持 双 BIOS 启动模式,可通过 BIOS_SEL 引脚的逻辑电平 选择启动源(计算模块内置 Flash 或载板上的外部 Flash)。 当 BIOS_SEL 引脚被拉低 时,LattePanda Mu 计算模块将绕过内部 Flash 芯片,从载板上的 SPI Flash 芯片启动。 该特性允许你将 定制 BIOS 固件 直接烧录到载板的 Flash 芯片中,而无需修改计算模块本身的 BIOS。 设计指南 引脚定义  启动源选择配置  BIOS_SEL 引脚内部集成 100K 上拉电阻。如果不需要使用载板 BIOS,该引脚可 悬空(NC),系统将默认从计算模块内置 Flash 启动。  器件选型  上电时序

启动选择电路 利用 BIOS_SEL 引脚内部的上拉电阻,可简化载板设计:

连接方式:

状态说明:

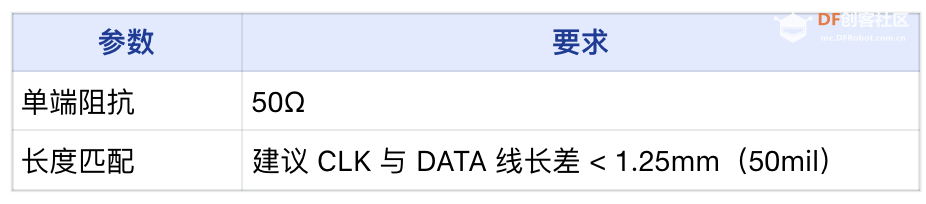

串联电阻 Intel 参考设计建议在 SPI 信号线上加入串联电阻(CLK、IO0~IO3):

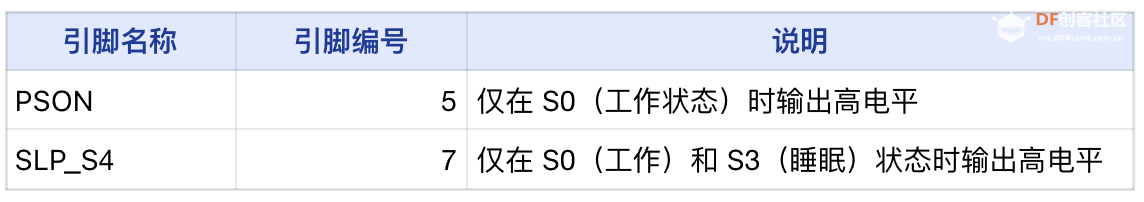

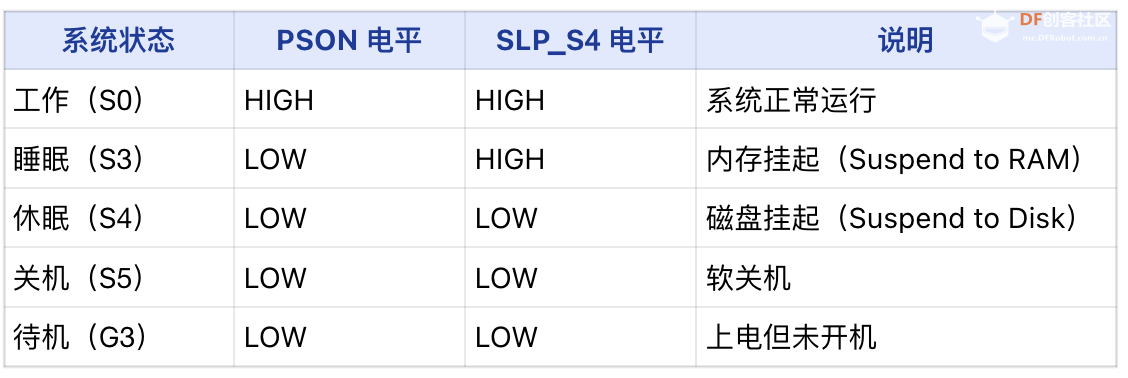

布局指南  LattePanda Mu 载板设计指南系列|电源控制与电源状态 本节聚焦电源控制与电源状态,介绍 LattePanda Mu 的电源状态指示与电源/复位控制信号,帮助你正确实现系统上电、关机、休眠状态管理及外设联动控制。 状态指示 LattePanda Mu x86 计算模块提供 PSON 和 SLP_S4 两个状态输出引脚,用于指示当前系统的电源状态(如 S0、S3 等)。这些引脚可用于控制载板外设的电源使能信号,或驱动状态指示 LED。 引脚定义  由于 PSON 和 SLP_S4 引脚的驱动能力有限,如需驱动 LED 指示灯,必须使用外部 NMOS 管进行驱动。 状态逻辑表  电源控制 LattePanda Mu x86 计算模块提供 电源键和复位键信号,其工作方式与标准笔记本或台式机完全一致。 引脚定义  PWR_SW# 连接物理电源按键,低电平有效 建议低电平脉冲时间 ≥ 125ms,以确保可靠识别 持续拉低 超过 4 秒 将触发强制关机 RST_SW#

ESD 保护 由于按键经常被人触摸,容易受到静电放电(ESD)影响,强烈建议在按键电路中增加 ESD 保护二极管。

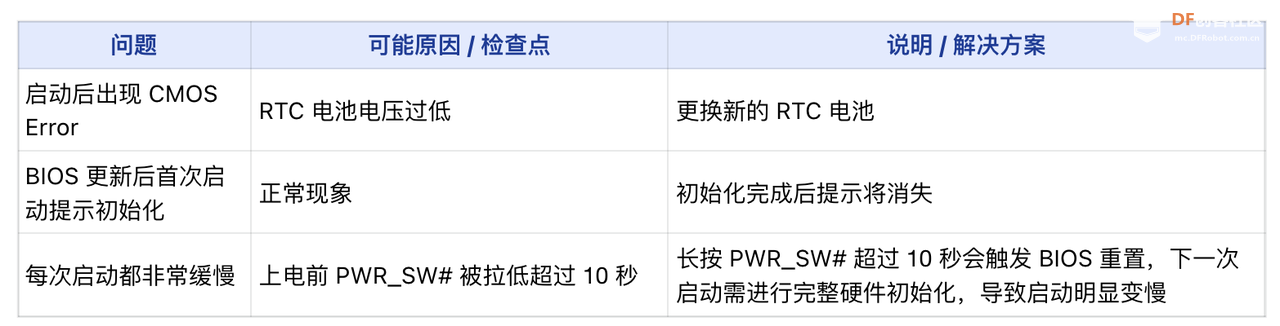

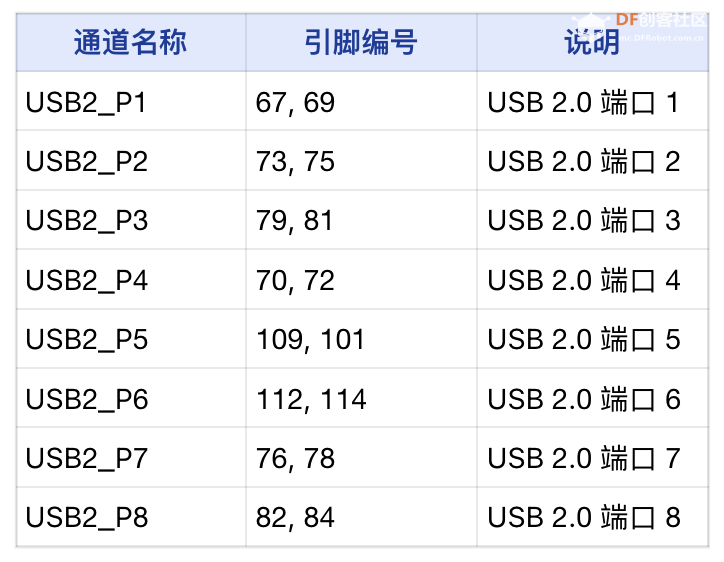

常见问题  LattePanda Mu 载板设计指南系列|USB 2.0 本节聚焦 USB 2.0 接口设计,介绍 LattePanda Mu 提供的多路 USB 2.0 通道配置、引脚定义及布线与 ESD 设计要点,帮助你实现稳定可靠的 USB 外设连接。 LattePanda Mu 最多提供 8 路独立的 USB 2.0 通道。

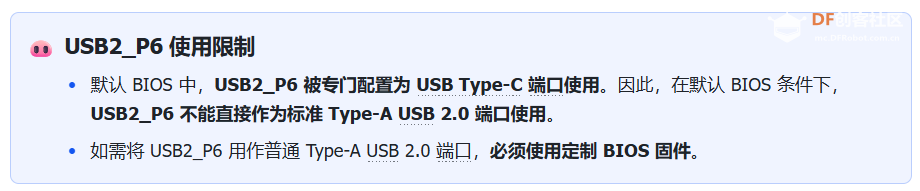

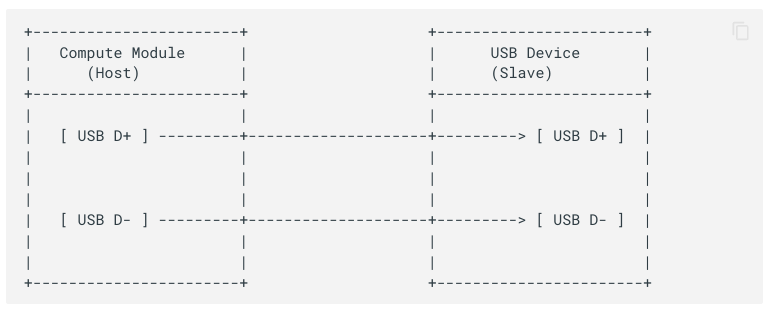

设计指南 引脚定义   USB2_P6 使用限制 默认 BIOS 中,USB2_P6 被专门配置为 USB Type-C 端口使用。因此,在默认 BIOS 条件下,USB2_P6 不能直接作为标准 Type-A USB 2.0 端口使用。 如需将 USB2_P6 用作普通 Type-A USB 2.0 端口,必须使用定制 BIOS 固件。 极性检查  USB 2.0 控制器 不支持差分对极性自动反转。

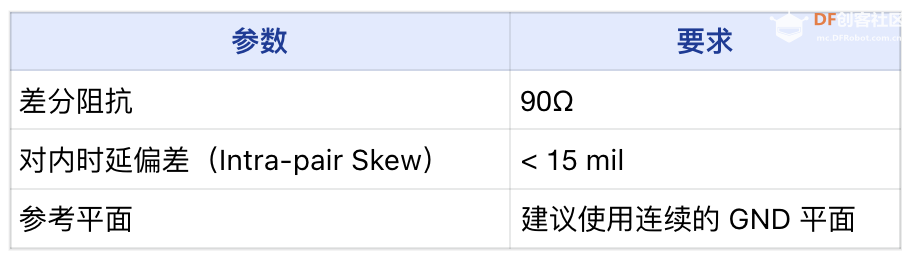

不使用 AC 耦合 禁止 在 USB 2.0 差分线上串联 AC 耦合电容。USB 2.0 信号必须直连。 ESD 保护 由于 USB 接口经常进行热插拔,极易受到静电放电(ESD)影响,强烈建议在数据线上添加 ESD 保护二极管。 推荐参数:

布局指南  LattePanda Mu 载板设计指南系列|USB 3.2 Gen 2 本节介绍 USB 3.2 Gen 2 接口设计,重点说明 HSIO 通道复用规则、BIOS 配置限制以及 10Gbps 高速信号在 AC 耦合、ESD 防护与布线上的关键设计要点。 LattePanda Mu x86 计算模块通过 HSIO(High Speed I/O)通道最多可引出 4 条 USB 3.2 Gen 2 通道,最高支持 10Gbps 的全双工传输速率,并向下兼容 USB 3.0(5Gbps)。 通道配置  USB 3.2 信号仅能从 HSIO0 ~ HSIO3 通道中复用。 默认 BIOS 配置中:HSIO 0 和 HSIO 1 已启用为 USB 3.2 通道。  注意

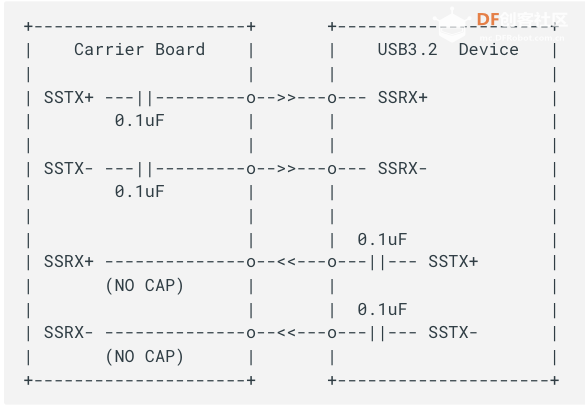

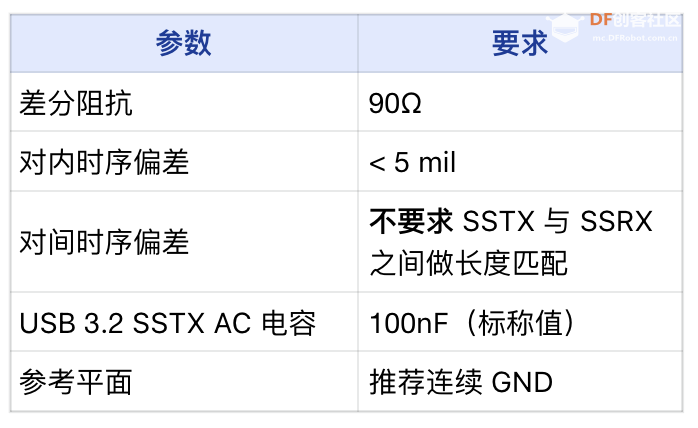

设计指南 引脚定义  AC 耦合 注意

设计要求

极性检查 Intel 的参考设计文档未明确确认 USB 3.2 差分对是否支持极性反转。因此,载板设计中应严格保持差分对极性一致(如上图所示)。 配对要求 标准 USB 3.2 Type-A 接口由两部分组成:

配对规则

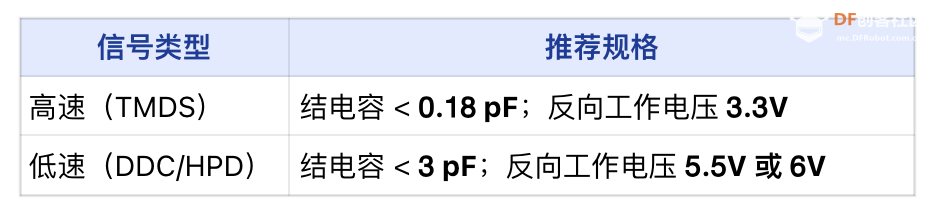

USB2_P6 限制说明 如 USB 2.0 章节所述:USB2_P6 默认保留用于 USB Type-C 接口,在未修改 BIOS 的情况下,不能作为 USB 3.2 接口的 USB 2.0 配对通道使用 ESD 防护 USB 接口频繁热插拔,极易受到静电放电(ESD)影响;同时 USB 3.2 的 10Gbps 高速信号对寄生电容极为敏感。 因此,必须使用超低电容 ESD 保护二极管。 推荐规格

布线指南  间距与串扰

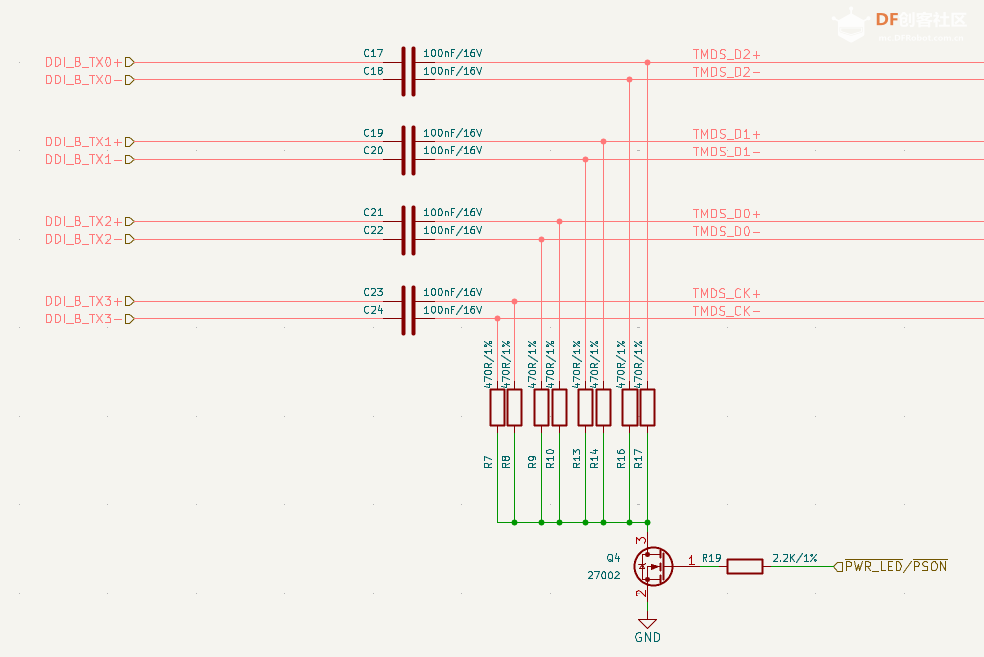

LattePanda Mu 载板设计指南系列| HDMI 2.1 本节介绍 LattePanda Mu x86 计算模块在 HDMI 2.1(TMDS 模式)下的接口能力与硬件设计要求,涵盖接口配置、原理图与 PCB 设计要点,确保 4K@60Hz 显示的信号完整性与兼容性。 LattePanda Mu x86 计算模块可通过 DDIB、TCP0 和 TCP1 接口最多派生 3 路 HDMI 输出,最高支持 4K home.php?mod=space&uid=886163 60Hz。 接口配置

注意 设计指南 引脚定义  AC 耦合与下拉偏置 注意 英特尔的参考设计需要特定的交流耦合+下拉偏置拓扑结构。

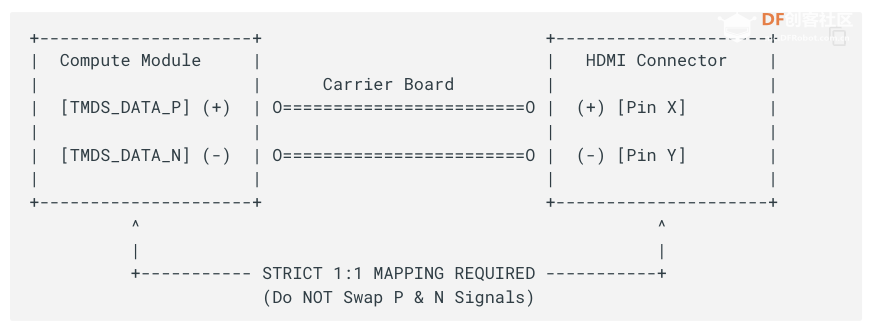

为什么必须使用 470Ω 下拉电阻? 极性检查 HDMI TMDS 差分对 不支持极性反转。 载板上必须严格执行极性匹配。确保正极 (+) 对应正极 (+),负极 (-) 对应负极 (-),如下图所示。  电平转换

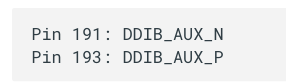

无 AUX 信号 在 TMDS 模式下运行时,AUX 信号未使用,因此应保持未连接状态。 例如,DDIB 工作在 TMDS 模式时,以下引脚需 NC:  ESD 保护 由于 HDMI 接口经常需要热插拔,因此容易受到静电放电(ESD)的影响。而 TMDS 信号对电容极其敏感,所以必须使用超低电容的 ESD 保护二极管。  布局指南  间距与串扰

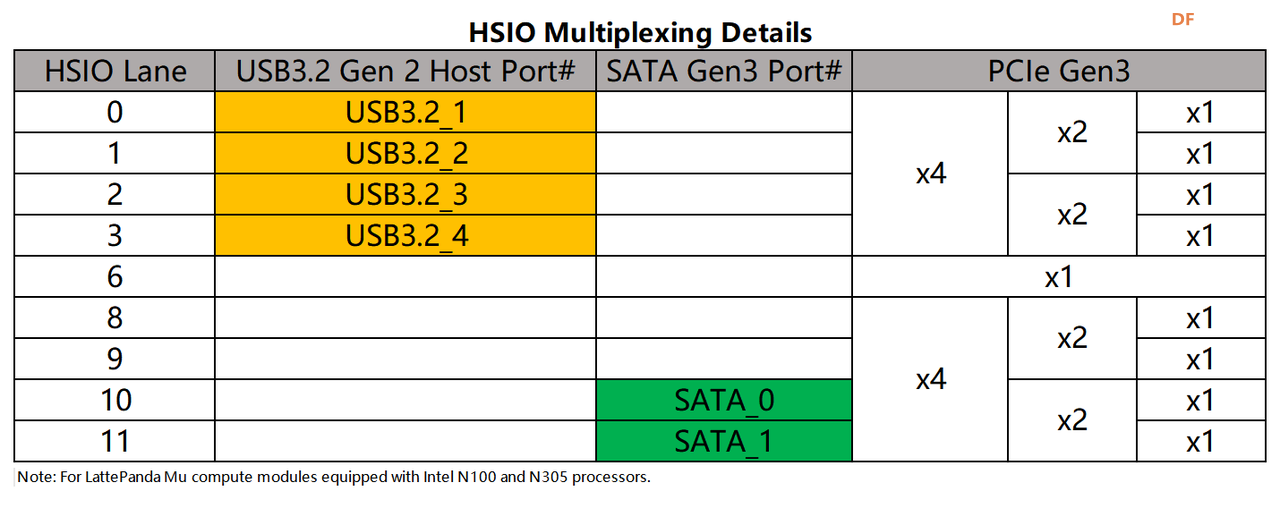

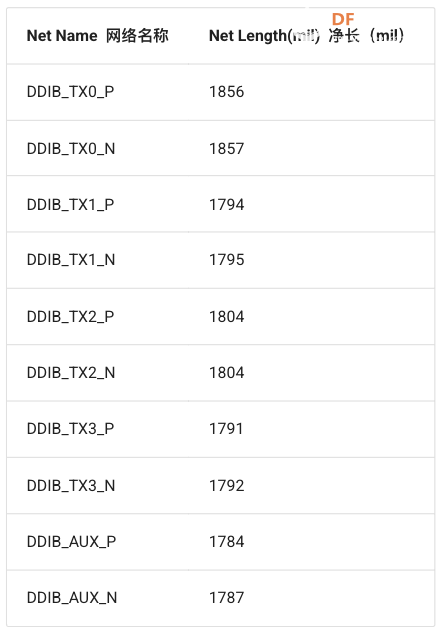

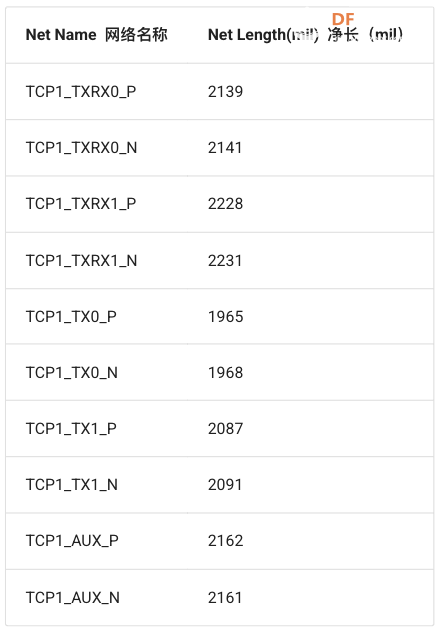

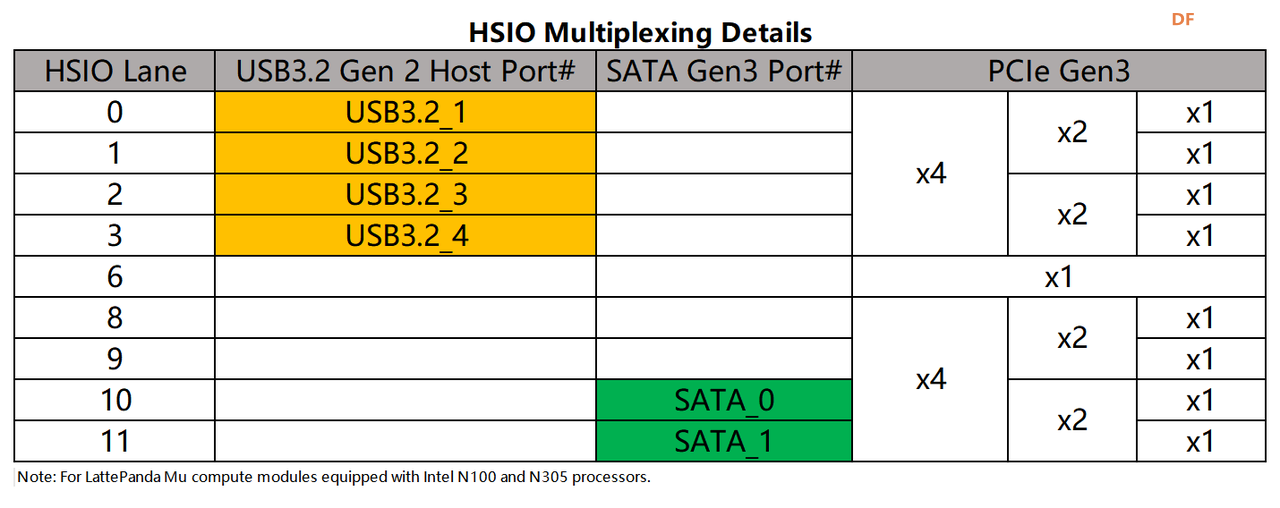

差分对网络长度 以下表格列出了 LattePanda Mu 计算模块的 DDIB、TCP0 和 TCP1 接口的轨道长度。    LattePanda Mu 载板设计指南系列| HSIO 通道复用与 PCIe 架构 本节详细说明 LattePanda Mu x86 计算模块的 HSIO 通道复用与 PCIe 架构,涵盖通道功能分配、PCIe 分叉规则、BIOS 配置限制以及 PCIe 时钟(REFCLK / CLKREQ)的绑定与设计注意事项,帮助载板设计者正确规划高速接口。 LattePanda Mu x86 计算模块从 Intel 处理器引出了 全部 9 条可复用 HSIO(High-Speed I/O)通道。这些通道具有高度灵活性,可根据载板设计需求配置为 USB 3.2、SATA 或 PCIe。  HSIO 复用规则 基于 Intel 硬件参考设计¹,各 HSIO 通道支持的功能如下:

PCIe 分叉 在 PCIe 模式下,HSIO 通道支持灵活的分叉配置。为便于理解,9 条 HSIO 通道被分为三组: HSIO 0 ~ 3

方案一:HSIO 0+1(x2)+ HSIO 2(x1)+ HSIO 3(x1) 方案二:HSIO 0(x1)+ HSIO 1(x1)+ HSIO 2+3(x2)

HSIO 8 ~ 11

方案一:HSIO 8+9(x2)+ HSIO 10(x1)+ HSIO 11(x1) 方案二:HSIO 8(x1)+ HSIO 9(x1)+ HSIO 10+11(x2)

混合配置 上述分叉规则适用于 整组通道全部用于 PCIe 的情况,但也支持 混合功能配置: 规则:配置为 USB 3.2 或 SATA 的通道将从 PCIe 通道池中移除。剩余通道仍可根据分组逻辑形成有效的 PCIe 链路。 例如: 如果 HSIO 0 和 1 设置为 USB 3.2,则剩余的 HSIO 2 和 3 仍可配置为 1x2 模式(一个 PCIe x2)或 2x1 模式(两个 PCIe x1)。 排他性与限制 HSIO 通道复用是互斥的 ,不支持运行时协议自适应。 固定功能: 一旦在 BIOS 固件中将通道配置为特定功能(例如 USB 3.2),它就固定用于该目的,不能自动切换到其他功能,例如 PCIe。 组依赖性: 在同一 PCIe 组内混合功能(例如,HSIO 0 ~ 3)会破坏 PCIe 链路聚合。 示例

应用配置变更 HSIO 通道分配和 PCIe 链路配置是静态的 。它们无法通过 BIOS 设置菜单进行配置,也不支持自动协商或运行时切换。 要应用更改,您必须按照以下步骤操作: 1.自定义 BIOS 固件以定义新的配置。 2.将更新后的固件重新刷写到 LattePanda Mu 模块(或载板上的闪存芯片)中。 3.然后重启 LattePanda 模块以使更改生效。 示例:(任何 HSIO 或 PCIe 通道拆分配置更改都需要定制 BIOS 固件。以下列出了一些常见示例。)

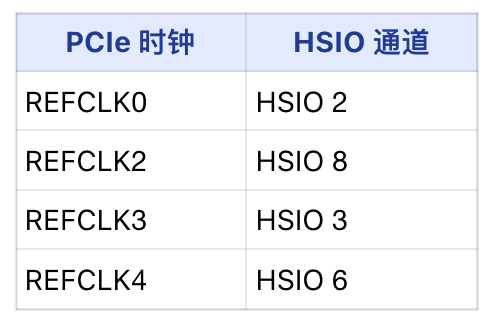

PCIe 时钟分配与扩展 LattePanda Mu 提供 5 路独立 PCIe REFCLK(参考时钟)。如果您的载板设计需要连接超过 5 个 PCIe 设备,则必须使用 PCIe 时钟扇出缓冲芯片来扩展时钟信号。 警告: 请勿尝试直接将单个时钟信号并行传输至多个设备。这样做会导致信号完整性问题,并最终导致设备识别失败。 CLKREQ 映射与控制 LattePanda Mu 计算模块仅公开两个 PCIe CLKREQ(时钟请求)引脚: CLKREQ3 和 CLKREQ4 。 这些引脚严格控制特定的参考时钟输出:

在默认 BIOS 配置下,对于缺少专用 CLKREQ 引脚的 REFCLK 输出:

时钟与 HSIO 通道绑定关系 BIOS 默认定义了 PCIe 时钟输出 (REFCLK) 和 PCIe 数据通道 (HSIO) 之间的特定绑定。  REFCLK1 为强制输出,不绑定任何 HSIO。 要修改时钟到通道的映射关系,需要定制的 BIOS 固件。无法通过 BIOS 设置菜单进行更改。 使用默认的 BIOS 固件,但更改载板上的此配对(例如,将 REFCLK 0 路由到 HSIO 8 上的设备)将阻止 PCIe 设备接收正确的时钟信号,从而导致枚举失败。 原因如下:

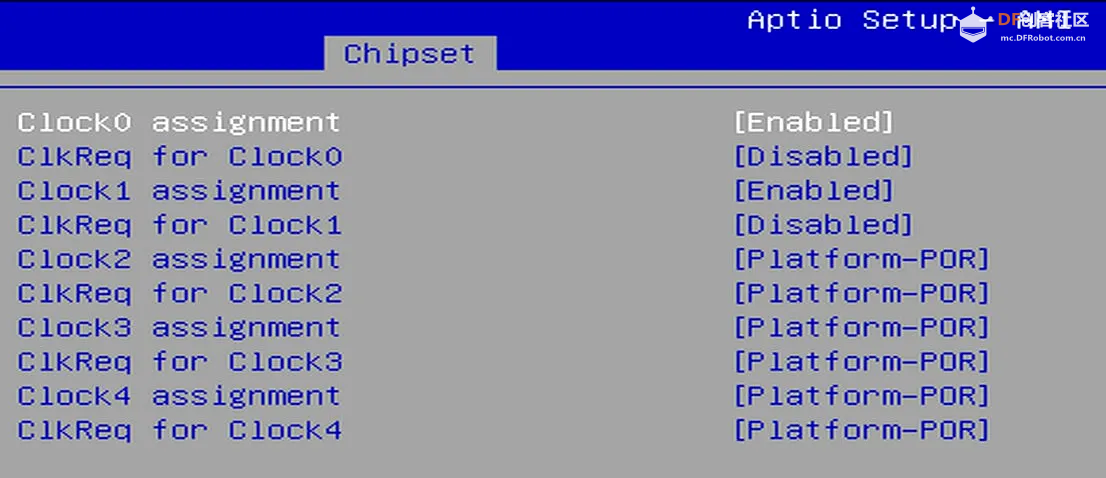

如果出现这种情况,您可以尝试在 BIOS 菜单中将相应的 REFCLK 设置为强制输出。大多数情况下,设备随后就能被正常识别。 例如,将 REFCLK0 设置为强制输出。

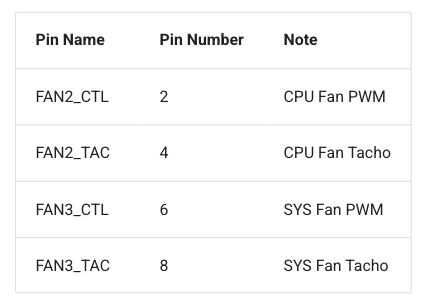

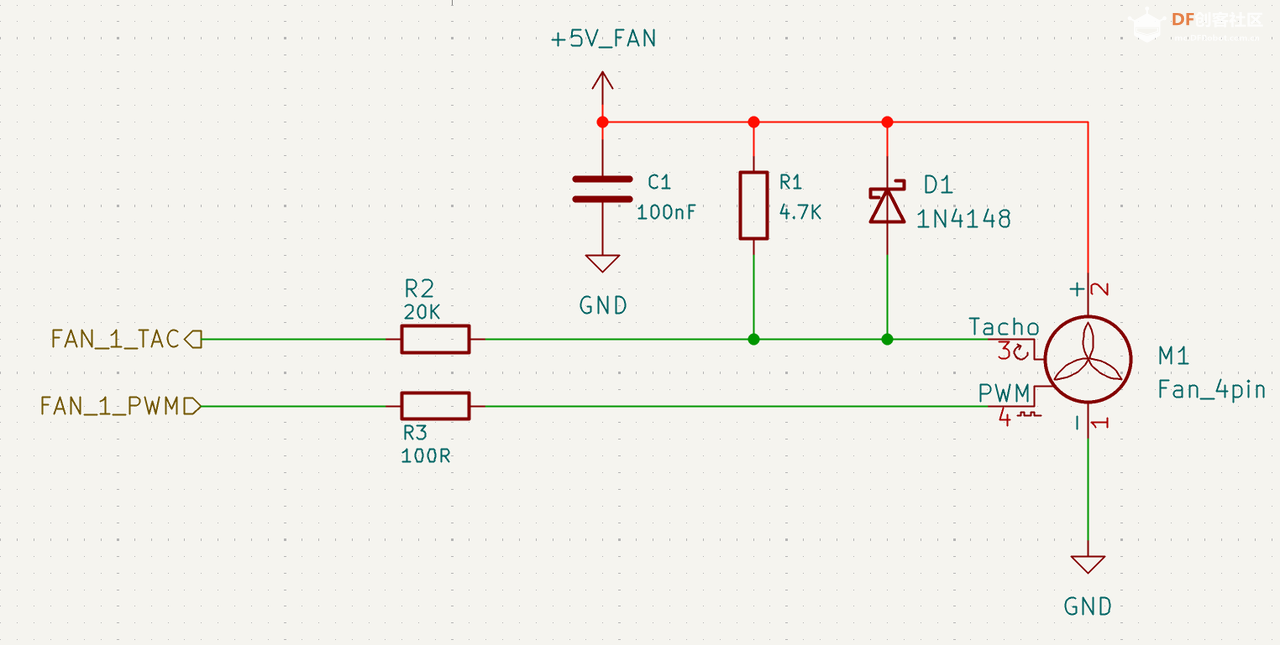

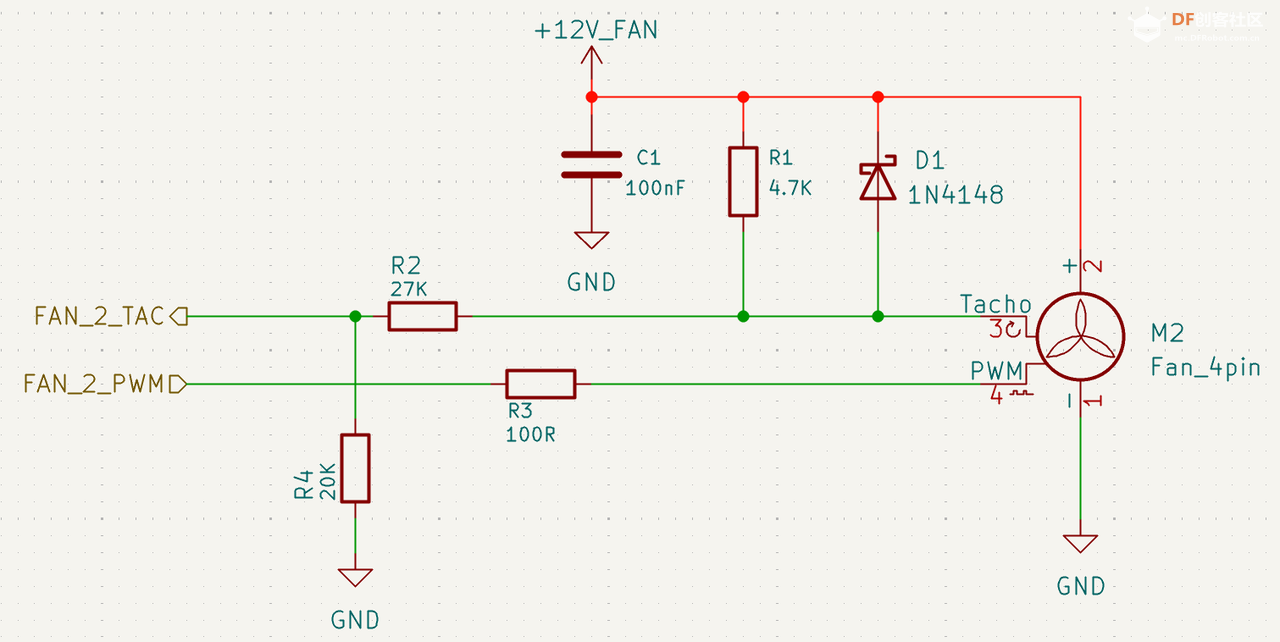

然后保存 BIOS 设置并重启。 如果上述步骤无法解决问题,则需要定制固件。 _ ¹ Intel® Processor and Intel® Core™ i3 N-Series Datasheet, Volume 1 of 2 _ LattePanda Mu 载板设计指南系列| 风扇 本节介绍 LattePanda Mu x86 计算模块的风扇接口设计与使用规范,涵盖 CPU_FAN 与 SYS_FAN 的 PWM 调速、转速监测机制,以及在载板设计中针对 5V 与 12V 风扇所需的上拉、电平限制与保护电路要求。 LattePanda Mu x86 计算模块提供两组独立的风扇接口,支持 PWM 转速控制和 RPM 转速监测(Tachometer)。其中 CPU_FAN 用于 CPU 散热风扇,SYS_FAN 用于系统或机箱风扇。 设计指南 引脚定义  PWM 信号 模块的 PWM 输出端已内置 4.7kΩ 上拉至 3.3V,无需在载板上额外上拉,但建议串联 100Ω 电阻进行限流。 转速表信号 TAC 引脚为开漏输入,需要外部上拉电阻和保护电路。其设计会根据风扇电压(5V 或 12V)而有所不同。 注意:所有 TAC 引脚只能承受 5V 电压! 关键设计规则 1.上拉源 :

建议将二极管 (例如 1N4148、1N5819)与上拉电阻并联。

3.层级转换 :

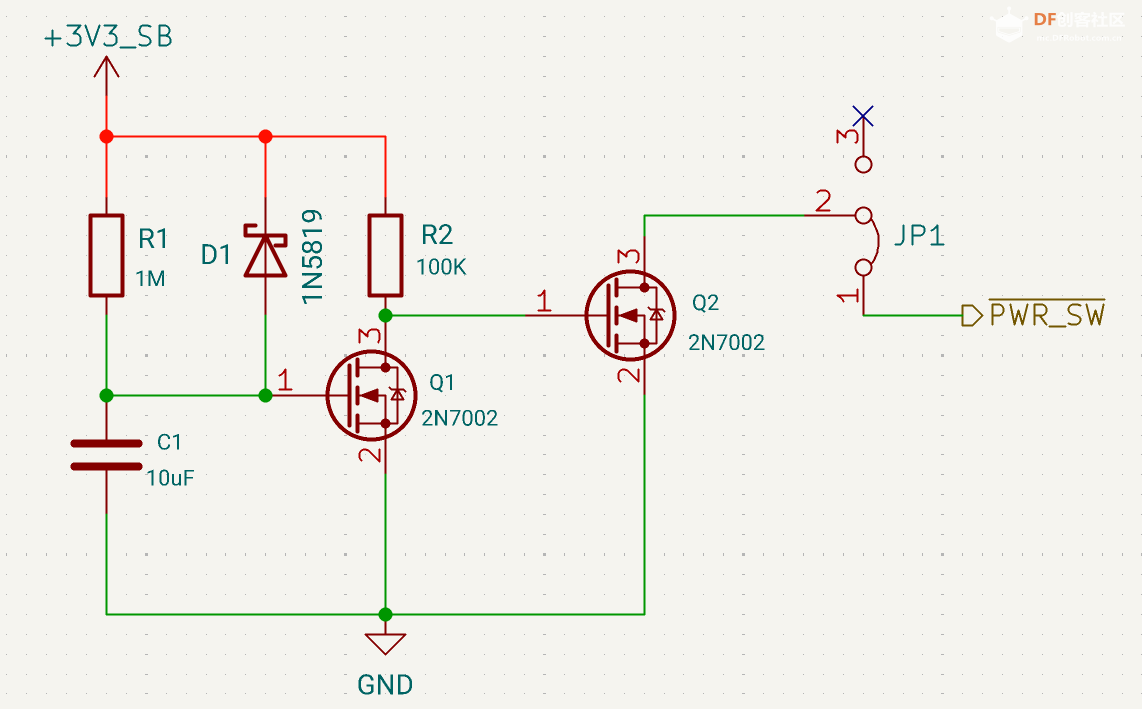

推荐风扇电路  5V 风扇:上图中,电阻 R2 可以选择 1K 到 30K 之间的阻值。如果空间有限,也可以省略该电阻。  12V 风扇: 上图中,电阻 R4 是分压电路的一部分,用于确保 TAC 输入引脚的电压不超过 5V,因此不可省略 。基于此原理,R2 和 R4 的具体阻值可根据实际情况进行调整。 LattePanda Mu 载板设计指南系列| 自动开机 为了确保 LattePanda Mu 计算模块在通电后自动启动,载板上需要外部硬件电路。

参考电路  电路原理 该电路的目的是在电气上模拟按下电源按钮的物理动作。 1.初始化 :载板通电后,电路立即激活。 2.操作 :将 PWR_BTN# (电源按钮)信号拉低特定持续时间(模拟“按下”),从而触发计算模块的启动序列。 3.释放 :延迟后,将 PWR_BTN# 释放回高电平(模拟“释放”)。 JP1 是一个跳线。当 JP1 接通时,自动上电功能启用。 电源要求 自动上电电路的电源必须为 3.3V 待机电压 。也就是说,载板插入主电源后,该 3.3V 电源必须立即工作。 |

萌萌哒新人

萌萌哒新人

活跃会员

活跃会员

编辑选择奖

编辑选择奖

沪公网安备31011502402448

沪公网安备31011502402448© 2013-2026 Comsenz Inc. Powered by Discuz! X3.4 Licensed